#### Design Automation for Streaming Systems

by

Eylon Caspi

B.S. (University of Maryland, College Park) 1996M.S. (University of California, Berkeley) 2000

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor John Wawrzynek, Chair Professor Edward A. Lee Professor Robert Jacobsen

Fall 2005

Design Automation for Streaming Systems

Copyright © 2005

by

Eylon Caspi

#### Abstract

Design Automation for Streaming Systems

by

Eylon Caspi

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor John Wawrzynek, Chair

RTL design methodologies are struggling to meet the challenges of modern, large system design. Their reliance on manually timed design with fully exposed device resources is laborious, restricts reuse, and is increasingly ineffective in an era of Moore's Law expansion and growing interconnect delay. We propose a new hardware design methodology rooted in an abstraction of communication timing, which provides flexibly timed module interfaces and automatic generation of pipelined communication. Our core approach is to replace inter-module wiring with streams, which are FIFO buffered channels. We develop a process network model for streaming systems (TDFPN) and a hardware description language with built in streams (TDF). We describe a complete synthesis methodology for mapping streaming applications to a commercial FPGA, with automatic generation of efficient hardware streams and module-side flow control. We use this methodology to compile seven multimedia applications to a Xilinx Virtex-II Pro FPGA, finding that stream support can be relatively inexpensive. We further propose a comprehensive, system-level optimization flow that uses information about streaming behavior to guide automatic communication buffering, pipelining, and placement. We discuss specialized stream support on reconfigurable, programmable platforms, with intent to provide better results and compile times than streaming on generic FPGAs. We also show how streaming can support an efficient abstraction of area, allowing an entire system to be reused with automatic performance improvement on larger, next generation devices.

Professor John Wawrzynek, Chair

Date

#### Acknowledgements

First and foremost, I owe an incalculable debt of gratitude to my wife, Denise, and children, Josh and Ross. They have seen me through all too many years of graduate school, late nights, busy weekends, conference trips, and deadlines. They picked me up every time I was down. Without them, this dissertation would not have been completed. Likewise, thanks to my parents, Ehud and Rachel, without whom this dissertation might never have begun. And thanks to the rest of the family, Amir, Heather, and Richard, for all their support when the going got tough.

I am indebted to a number of advisors and mentors. Thanks to my research advisor, John Wawrzynek, for supporting this exciting course of research, and for making sure we always had industry visibility. Thanks to professor Edward Lee for a brilliant course on concurrent models that helped center my work, and for advising on this dissertation. Thanks to my external committee member, professor Bob Jacobsen, for encouragement and for keeping this dissertation honest and accessible. Thanks to Seth Goldstein (CMU) for profound comments that forever improved my technical presentations. Thanks to Carl Ebeling (U. Washington) for helping me find my way between academia and industry. Thanks to Kees Vissers for guidance and encouragement, both technical and practical, at Berkeley and during my time at Chameleon Systems.

Extra special thanks goes to André DeHon (CalTech), who has been a mentor and a friend for years. During his post-doc at Berkeley, André co-founded our research group, taught our first course on reconfigurable computing, and guided the SCORE project. Even after his departure, he continued to provide technical and personal guidance, as well as compute resources for the experiments in Chapter 4. Perhaps the strongest compliment to him is my having been dubbed *Mini André*.

Thanks to all the past and present members of the BRASS research group, and particularly to those on the SCORE project, without whom my work would not exist. Thanks to Michael Chu, Randy Huang, Yury Markovskiy, Laura Pozzi, and André DeHon for building the SCORE software base. Special thanks to Joe Yeh, who valiantly wrote our entire suite of multimedia applications in a strange (and often broken) language, TDF. Thanks to Nick Weaver for helping to turn me onto reconfigurable in the first place. Thanks to John Hauser and Tim Callahan for being mentors. Thanks to Norm Zhou, Kip Macy, Yujia Jin, James Yeh, and all the other occupants of our cozy office, 441 Soda, for making my years at Berkeley so much fun. Thanks to Jon Kuroda for keeping our computers from becoming door stops. Thanks to the BRASS group's industry liaisons, especially Steve Trimberger (Xilinx), for keeping a watchful eye on us. And thanks to DARPA, NSF, California Micro, Xilinx, and STMicroelectronics for funding our work.

Additional thanks goes to the IC group at CalTech, including Michael Wrighton, Michael Delorimier, Rafi Rubin, Helia Naeimi, Nachiket Kapre, and Stephan Lavavej. They carried the torch in the later days of SCORE, gave me many good ideas, and stress tested TDF with new applications. Likewise, thanks to Osvaldo Colavin, Antoine Hue, and others at STMicroelectronics, who evaluated and tested our software.

Thanks to Steve Neuendorffer and Jörn Janneck (Xilinx) for numerous discussions about process network theory. Thanks to Tero Rissa for helping SCORE (and me!) get to Finland. Thanks to everyone who fed the "starving" graduate students, including the computer science social hour, countless industrial recruiting sessions, and our favorite hangouts, Bongo Burger, LaVal's, La Burrita, and Seven Palms. Thanks to the U.C. Regents for making Berkeley a great place to study.

And finally, thanks to all the wives (and husbands) of the people mentioned above, who went out of their way every day to make our work possible.

For my wife, Denise, and our children, Josh and Ross

# **Contents**

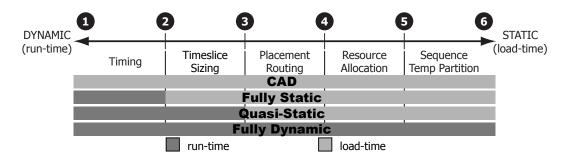

| 1        | Intr | roduction                                  | 1  |

|----------|------|--------------------------------------------|----|

|          | 1.1  | System Design Challenges                   | 1  |

|          | 1.2  | Limitations of RTL                         | 4  |

|          | 1.3  | Timing Tolerant System Composition         | 6  |

|          | 1.4  | Stream Based Design                        | 9  |

|          | 1.5  | Related Streaming Models and Architectures | 15 |

|          | 1.6  | Contribution and Organization              | 22 |

| <b>2</b> | Lan  | guage and Theoretical Foundation           | 24 |

|          | 2.1  | Streaming Models                           | 25 |

|          | 2.2  | TDF Process Networks                       | 30 |

|          | 2.3  | TDF Language                               | 38 |

|          | 2.4  | TDFPN Denotational Semantics               | 54 |

| 3        | Syn  | thesis Methodology for FPGA                | 73 |

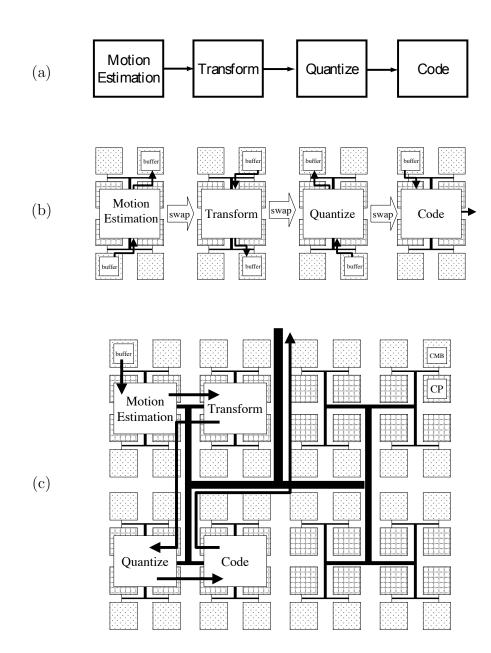

|          | 3.1  | Compilation Flow                           | 74 |

|          | 3.2  | Stream Protocol                            | 77 |

|          | 3.3  | SFSM Synthesis                             | 77 |

|          | 3.4  | Queue Implementation                       | 80 |

|          | 3.5  | Streaming Memories                         | 86 |

|   | 3.6                       | System Composition            | 87  |  |  |

|---|---------------------------|-------------------------------|-----|--|--|

|   | 3.7                       | Stream Enabled Pipelining     | 89  |  |  |

| 4 | Characterization for FPGA |                               |     |  |  |

|   | 4.1                       | Experimental Setup            | 97  |  |  |

|   | 4.2                       | Applications                  | 99  |  |  |

|   | 4.3                       | Baseline Results              | 107 |  |  |

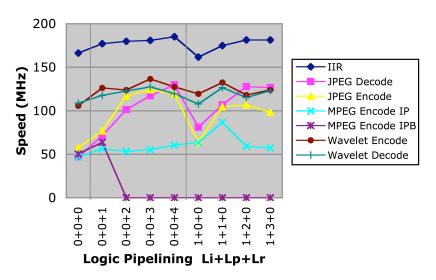

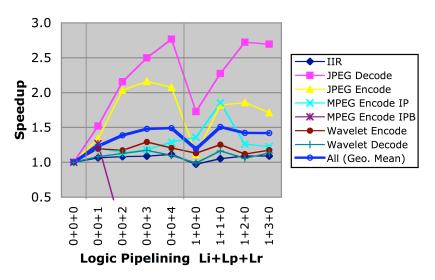

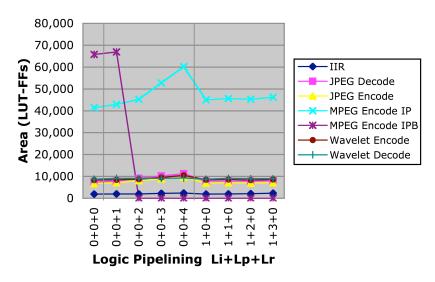

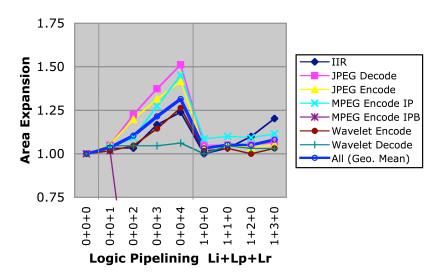

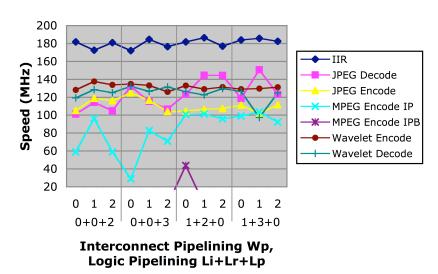

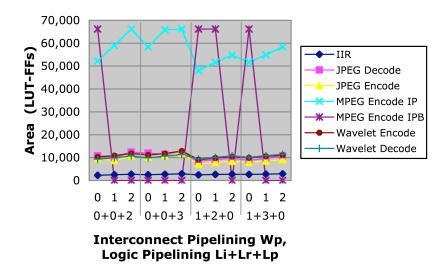

|   | 4.4                       | Logic Pipelining              | 114 |  |  |

|   | 4.5                       | Interconnect Pipelining       | 128 |  |  |

|   | 4.6                       | Summary                       | 144 |  |  |

| 5 | Sys                       | tem Optimization              | 147 |  |  |

|   | 5.1                       | System Optimization Flow      | 150 |  |  |

|   | 5.2                       | Stream Buffer Bounds Analysis | 153 |  |  |

|   | 5.3                       | Stream Aware Placement        | 183 |  |  |

|   | 5.4                       | Process Pipelining            | 193 |  |  |

|   | 5.5                       | Pipeline Balancing            | 194 |  |  |

|   | 5.6                       | Serialization                 | 201 |  |  |

| 6 | Stre                      | eaming Programmable Platforms | 204 |  |  |

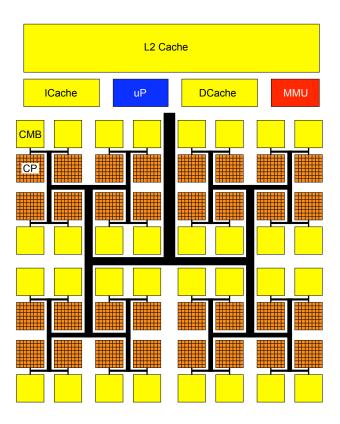

|   | 6.1                       | Basic Platform                | 207 |  |  |

|   | 6.2                       | Paged Platform                | 215 |  |  |

|   | 6.3                       | Virtual Paged Platform        | 221 |  |  |

|   | 6.4                       | Page Partitioning             | 238 |  |  |

| 7 | Conclusion 2              |                               |     |  |  |

|   | 7.1                       | Summary                       | 254 |  |  |

|   | 7.2                       | Open Questions, Future Work   | 258 |  |  |

| 7.3          | History and Relation to SCORE | 265 |  |  |

|--------------|-------------------------------|-----|--|--|

|              |                               |     |  |  |

| Bibliography |                               |     |  |  |

# Chapter 1

# Introduction

## 1.1 System Design Challenges

The design of modern computational systems is driven by an incessant market demand for systems to have more functionality, be faster, be smaller, last longer on battery, and be cheaper. The industry's success in meeting such a tall order has been fueled by Moore's Law, namely the uncanny ability of process engineers to put more transistors on a chip each year. Technology improvements in recent years have reduced feature sizes on chip by an average of 11%-16% per year, leading to improvements in clock rates and to a doubling of transistor capacity every 1.5 to 2 years [ITRS, 2003].

Moore's law improvements also bring a host of difficulties associated with large system design and deep sub-micron (DSM) effects. Today's largest systems involve tens of millions of gates, or hundreds of millions of transistors<sup>1</sup>, necessitating a highly modular design methodology and large teams of up to hundreds of engineers. One of the greatest design challenges is the growing dominance of interconnect delay, which owes to disproportionate improvements in wire speed versus logic speed at each technology generation [Agarwal et al., 2000] [Sylvester and Keutzer, 1999]. Designers

are forced to pipeline deeper to meet target clock rates, complicating designs further. The large and often unpredictable impact of distance on performance leads to an insidious timing closure problem, where design modifications intended to improve performance may actually diminish it due to changes in area and layout. These trends, and the inability of design automation tools to keep up, have resulted in a design productivity gap, where the number of transistors available on chip is growing 58% per year, but the number of transistors programmed per man-month is growing only 21% per year [ITRS, 1999].

Programmable platforms, such as field programmable gate arrays (FPGAs), have emerged as a popular alternative to application specific integrated circuits (ASICs). Since they are off-the-shelf components, FPGAs free system designers from many of the DSM effects involved in transistor level chip design, including parasitics extraction, crosstalk, signal integrity, clock distribution, and electromigration. FPGA based design also avoids the high cost of mask production for chip fabrication. Modern, high capacity FPGAs can emulate millions of logic gates using software programmable look-up tables, so they can accommodate a significant number of real world designs. Furthermore, due to their regularity, FPGAs tend to be early adopters of new technology generations, bringing with them the promise of technology scaling without the cost of fabricating a chip. Unfortunately, with such large device sizes, FPGA based design suffers from many of the same large system and DSM effects as ASIC design, including high design complexity, growing interconnect delay, and long run-times for tools such as place-and-route. For example, routing typically accounts for 45%-65% of the critical path on an FPGA [Xilinx, 2003a]. Thus, a productivity gap remains.

Despite the growing complexity and cost of system design, systems are regularly discarded and redesigned with each new device generation. Hardware design method-

$<sup>^1</sup>$  Some multi-million transistor systems—AMD Athlon 64 X2: 233M transistors [Mitchell, 2005], IBM Cell: 241M transistors [Gschwind *et al.*, 2005], nVidia GeForce 7800 GTX: 302M transistors [Kirk, 2005].

ologies tend to be very tied to the specific sizes and timings of a device. Consequently, significant redesign is necessary to take full advantage of the greater area on a new device, and to deal with disproportionate changes in logic and interconnect delays. Engineers strive to reuse at least some modules of a design, but this reuse does not mitigate the need for system redesign. The effort for engineering a system is not only growing, it is being largely repeated from scratch.

Microprocessor architectures have allowed some designers to press on, blissfully unaware of DSM difficulties and the productivity gap. Such architectures are programmed using instruction set architectures (ISA) that abstract away the underlying circuit implementation. This abstraction also allows microprocessor software to survive and scale on compatible, next generation processors, riding Moore's Law to better performance. However, processor based systems have limited performance and limited density (in terms of performance-per-dollar or performance-per-watt), so they cannot serve the entire market. The loss in density comes from supporting the ISA abstraction, and increasingly from extra area devoted to parallelizing instruction streams and overcoming long interconnect delay (e.g. large caches to hide memory access latency). It is predicted that future improvements in microprocessor performance will be strictly limited by interconnect delay, which limits the amount of state accessible in each clock cycle Agarwal et al., 2000. To continue improving performance, designers will be forced to abandon the trend towards larger, more complex microprocessors, and instead consider more parallel architectures. Already today, many systems-onchip (SoC) combine one or more simple processors with many other cores, and their designers are forced to deal with the hard issues of chip design.

We contend that many of the difficulties in modern system design stem from the prevalent use of register transfer level (RTL) design methodologies, which fully expose device timing. To increase productivity and design longevity, we must consider new abstractions that hide or otherwise assist in dealing with technology limiters such as interconnect delay and area. To this end, we shall propose an abstraction of timing based on *streams* as a replacement for long wires. We shall also show how streams support an efficient abstraction of area, given proper architectural support. These abstractions will be supported and enforced by a language and an automatic compiler for hardware. The abstractions enable a number of system-level analyses and optimizations that are not possible in RTL-based design, which serve to improve designer productivity and to promote reuse, retargeting, and scaling.

#### 1.2 Limitations of RTL

The prevalent design abstraction for digital systems today is the register transfer level (RTL) description, which specifies a timed signal flow through logic and registers. For the sake of discussion, we distinguish the term timing, referring to picosecond measures such as signal delays and setup and hold times, from timing behavior, referring to integer measures of machine cycles. An RTL description fully specifies the timing behavior of a circuit, i.e. the cycle by cycle schedule of computation and communication. The design philosophy of RTL is that, to achieve a target clock rate, timing should be predictable and exposed to the designer, and the designer should manually pipeline the circuit accordingly. Design methodologies have improved by abstracting from structural descriptions, involving netlists of logic and registers, to behavioral descriptions, involving state machines. However, the basic paradigm of fully specified timing behavior persists.

The growing dominance of interconnect delay on chip poses a serious difficulty for RTL based design, since it makes timing unpredictable. For larger circuits, signal delays become dependent on placement, which is normally determined only after synthesis from RTL. Thus, it is not obvious how to best pipeline a circuit and choose its timing behavior. The industry has attempted a number of approaches for improving

timing predictability in large circuits, with limited success. Making placement explicit before RTL, *i.e.* floorplanning, is possible but requires significant design effort. Physical synthesis attempts to feed timing information from placement back to guide RTL transformations and resynthesis. However, its improvement on clock rate is limited (e.g. 5%-20% in Synplify Premiere [Synplicity, 2005b]), since it is not allowed to introduce new pipeline stages or to modify visible timing behavior. Retiming can be modified to consider interconnect delay by performing it during [Singh and Brown, 2002] or after [Weaver et al., 2003] placement, but it too is not allowed to introduce new pipeline stages or to modify visible timing behavior. The delays in question grow with each device generation, so ultimately, deeper pipelining is a necessity.

Large RTL designs are typically decomposed into small modules. On the surface, this seems to improve timing predictability, since inside a small module, interconnect delay would remain small and predictable. However, this approach merely exports the problem to the level of inter-module connections, which themselves need to be pipelined. Pipelining inter-module connections is usually not straightforward, since it breaks the expected timing behavior of module interfaces. In the fully-timed world of RTL design, a module's internal behavior is coupled to its communication behavior, which in turn is coupled to the behavior of other modules and the entire system. The use of modules as design units, in and of itself, does nothing to decouple the modules in time and nothing to address interconnect delay. In this sense, the philosophy of fully timed RTL design is actually obstructive to modularity—it limits module reuse in new timing environments, and it prevents modular optimizations that modify an individual module's timing behavior. A truly modular design methodology must be more tolerant of changes in timing behavior.

## 1.3 Timing Tolerant System Composition

Believing that predictable timing is a lost cause, there are a number of efforts to make timing more abstract to the designer. Most are based on timing tolerant interfaces between modules.

#### 1.3.1 Asynchronous Circuits

Asynchronous circuits take timing tolerance to the extreme by removing clocks altogether and using handshaking to tolerate any delay. As a consequence, asynchronous circuits accommodate pipelining by simple insertion of half buffer elements [Lines, 1995]. Unfortunately, asynchronous circuits are not well supported by design tools, and they incur an area penalty for handshaking. A more practical approach is to introduce handshaking and asynchrony only at a coarser granularity, between modules. The GALS (globally asynchronous locally synchronous) approach involves conventional, synchronous design within modules and pipelined, asynchronous interconnect between modules. With this two-level hierarchy, interconnect between modules may be packaged as IP (intellectual property) or as a network on chip (NOC), e.g. Nexus [Lines, 2004].

#### 1.3.2 Synchronous Standard Interfaces

It is not necessary to resort to asynchronous circuits in order to decouple the timing behavior of modules. A purely synchronous handshaking protocol would suffice. Several system on chip (SOC) interconnect standards exist which use such handshaking, including CoreConnect [IBM, 1999], AMBA [ARM, 1999], and OCP [OCP, 2001]. Such standards provide conventions for module interfaces, along with IP blocks to implement inter-module transport. However, only some packages provide a pipelined

transport to enable long distance communication at high clock rates, e.g. the SONICS SiliconBackplane implementation of OCP [Sonics, 2005] point-to-point links.

A mere specification of interface conventions, as in the standards above, is only slightly better than none at all. It puts the burden of conforming to the interface on the module designer, including writing a state machine to sequence all the required signals. It also puts the burden of choosing interconnect implementation parameters on the designer, including pipelining depth, queue size, bit width, and so on. These manual choices ultimately obstruct reuse, since they must be reconsidered when porting to a next generation device, and changes may require reimplementation of modules. Making reuse practical would require standard interface packages to provide automation for choosing interconnect parameters and for regenerating module interfaces. Our streaming design methodology does provide that automation.

#### 1.3.3 Latency Insensitive Design

Latency insensitive design (LID) [Carloni et al., 2003] [Carloni et al., 2001] is a more transparent approach to system composition, providing automatic inter-module pipelining without handshaking or modification of modules. Pipelining inter-module wires changes the arrival time of signals, and may cause the inputs of a module to arrive out of phase. To retain correct behavior, LID specifies that a module must stall until a complete, matched set of its inputs has arrived. Each module is embedded in a shell that stalls the module via clock gating and provides queueing to realign inputs in time. The required queue depths and schedule of stalls are in fact static and fully predictable from the interconnect pipelining depths. Thus, the process of choosing pipeline depths and programming the shells can be performed automatically after placement. This design methodology successfully avoids the reduction in clock rate associated with long distance, inter-module communication. Nevertheless, the

addition of pipelining on feedback paths incurs a loss of throughput (data per clock period) and hence, a loss of system performance. This loss manifests easily on module interfaces that include feedback or hand-shaking, such as ready signals, and prevents those interfaces from operating at full throughput. Thus, for communication styles beyond simple, unidirectional wiring, LID may exacerbate rather than alleviate the effect of long interconnect.

In principle, it is possible to pipeline a handshaking protocol across a long distance at full throughput by relaying it. Rather than connecting two modules directly, a module may be connected to a protocol relay block that implements the same handshaking protocol. The relay buffers and retransmits transactions to another relay or to the target module. The first module may then go about its business, without waiting for the round trip delay of handshaking directly with the target module. Modules are thus decoupled in time, and each module is capable of transmitting or receiving at full throughput. This technique is used in asynchronous half buffer insertion, SONICS point-to-point links, as well as our own stream protocol. In contrast, LID relays raw wires rather than protocols. It transforms a system at too low a level to know that a protocol is being disturbed, so it cannot guarantee full throughput communication.

## 1.3.4 Bluespec

Bluespec [Bluespec, 2005] and its underlying term rewriting system [Arvind et al., 2004] [Hoe and Arvind, 2004] provide a different approach to timing tolerant system composition. Their basic abstraction is that of global state being updated by guarded, atomic actions, termed rules. Rules may be local to a module or may relate the state of several modules, inferring communication. Thus, communication and synchronization between connected modules need not be specified as timed behaviors, like RTL, but are derived automatically from rules. Concurrency comes from evaluating all rules

and applying as many non-conflicting actions as possible in each clock period. Timing tolerance comes from the allowance that an action may be deferred for several cycles, including an action that infers communication. Synthesis automatically generates all guard logic, interlock logic to prevent conflicting actions, and wiring between modules. To promote modular design and module reuse in Bluespec, a module's state is hidden behind *interface methods*, and modules communicate by invoking each others methods. In synthesis, those methods become guarded by the composition of rules across connected modules. The performance of a system depends on the combinational delay in the inferred composition of guards and actions, including inter-module wiring.

Unfortunately, pipelining in Bluespec remains a completely manual effort. Pipelining a module requires explicitly specifying new state for pipeline registers and factoring rules to use them. Likewise, decoupling inter-module connections in time requires declaring interface registers, queues, or some other intermediate, stateful elements. Specifying and exploring connection styles is substantially easier in Bluespec than in RTL. However, Bluespec does little to address growing interconnect delay. In fact, its reliance on analyzing global state is arguably obstructive to that end.

## 1.4 Stream Based Design

We seek a minimal set of abstractions beyond RTL to tackle some of the issues above concerning large systems, long interconnect delay, and design reuse. Our fundamental approach is to replace inter-module wires with *streams*, a particular form of buffered channels. Streams abstract communication timing, making a system more robust to delay, and supporting better modular design through timing-flexible interface specifications. Streams also abstract communication implementation, so they are amenable to automatic generation of efficient handshaking, transport, and buffering. Streams

represent dataflow between modules, not mere protocols, so they enable a compiler to perform more system level analyses and optimizations. With language and tool support, a streaming system can be automatically retargeted to next generation process technologies or programmable devices, thus enabling entire system reuse.

We briefly describe our streaming model here, chiefly in the context of technology trends and design productivity. More complete specification of the model and its language are provided in Chapter 2.

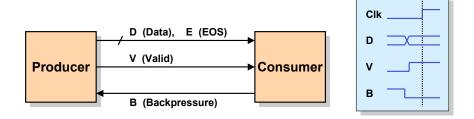

#### 1.4.1 Streaming System Composition

Modules are connected by a *stream* communication mechanism. A stream is a point-to-point, unidirectional, first-in-first-out (FIFO), buffered channel, which behaves as an ordered queue. A stream decouples its producer and consumer in time, up to the capacity of the stream queue. Flow control handshaking may be implemented by a simple pair of producer-ready / consumer-ready signals. A stream is easy to pipeline across long distances using protocol relaying or direct wire pipelining, yet it is still capable of transmitting at full throughput (we demonstrate a pipelined stream implementation in Chapter 3). In this sense, our approach provides a system composition methodology similar to OCP [OCP, 2001].

## 1.4.2 Timing Independence

We impose an additional constraint on streaming to guarantee timing independent system behavior. If an input desired by a module is not available, the module must stall. Specifically, the module may not test for input readiness and decide to do something else while waiting, since that may lead to timing-dependent behavior. The resulting system is a *process network* with *blocking read*, a formalism which has been proven to have deterministic behavior regardless of timing and scheduling [Kahn,

1974]. Thus, system correctness is ensured regardless of placement distance, stream pipelining, or stream implementation. Furthermore, system correctness is ensured regardless of any modification to the timing behavior of individual modules. A module may be pipelined or otherwise optimized, changing its timing behavior, without affecting system correctness or requiring modification of other modules. Thus, we support better modular design.

#### 1.4.3 Language Integration

Requiring the module designer to conform to a stream protocol is laborious and error prone. Instead, we provide language support and automation for streaming. We turn the stream into an abstraction, expose it as an object in the syntax of a hardware description language, and implement it through synthesis. A compiler can then automatically generate handshaking signals and stall control for each module. Automatic generation of communication saves labor and is correct by construction. It also ensures conformance to the streaming discipline and the process network model. Thus, it enables compiler analyses and optimizations that might not be practical or permissible on an unrestricted RTL description.

## 1.4.4 Automatic Module Optimization

Since stream communication is robust to timing, a compiler is free to implement optimizations that change the timing behavior of a module. Such optimizations may include pipelining, rescheduling, area-time transformations, or changes of granularity (module decomposition/merging). We present a number of specific module optimizations throughout this document. In Chapter 3, we discuss a simple, automatic approach to module pipelining (applicable not only in our language but to any RTL module that conforms to our stream protocol, since it is based on retiming registers

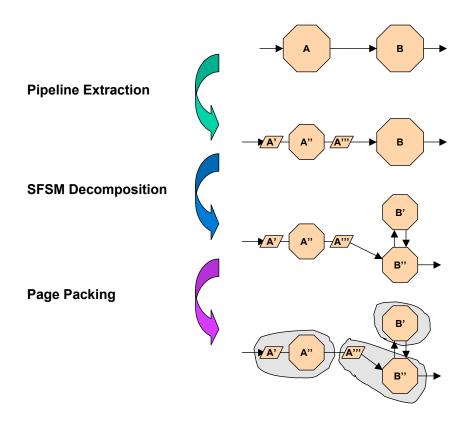

from streams). In Chapter 5, we discuss automatically implementing non-critical modules with serial arithmetic. In Chapter 6, we discuss automatically decomposing a large module into a collection of smaller, stream connected modules.

#### 1.4.5 Automatic System Optimization

The stream topology of a system exposes its communication dependencies, and thus its available parallelism. A compiler can use this information to implement global optimizations such as stream pipelining, stream queue sizing, area-time tradeoffs, and throughput-aware placement. Such optimizations would not be possible in RTL based design, where system level information is limited, and changes in timing behavior are not tolerated. An RTL description binds a particular level of parallelism into its timed description, and it does not provide enough information for a compiler to make reliable, large scale changes. A streaming design has more information and more freedom. We present a number of specific, system-level optimizations in Chapter 5.

#### 1.4.6 Reuse and Retargetting

The timing independent nature of streaming, as defined above, naturally supports better modular design and module reuse. Whereas an RTL module interface is specified in terms of timing behavior, a streaming module interface cares only about relative order of tokens. Consequently, a streaming module works in more contexts. A streaming module will continue to work on a next generation device that has different interconnect delay, where streams are pipelined deeper. More interestingly, a streaming module will work even if the transport implementation is changed, be it point-to-point wires, shared bus, or even shared memory. Modules may be optimized, independently or in concert, to better match the different timing and resources of a new device. Language integration can help automate the retargeting process by ap-

plying system level optimizations and regenerating both modules and streams. Thus, a streaming discipline with language integration supports entire system reuse, not just module reuse.

#### 1.4.7 Platform Support

It is possible to provide specialized resources for streaming on a programmable platform. A streaming platform might provide a network on chip (NOC) for stream

transport, custom stream queues, specialized programmable logic for stream handshaking, and streaming memory controllers. Any of these resources may be improved

in a next-generation device, provided their stream interface is retained. Additionally, streaming modules may be implemented in specialized computational resources,

such as MACs (multiply-accumulate), FFTs (fast Fourier transform), or microprocessor cores, provided they are equipped with streaming interfaces. Chip I/O may

be incorporated in special, streaming nodes, which translate from the on-chip stream

protocol to standard, off-chip protocols. Thus, a stream discipline can be the foundation for a complete system on a chip (SOC) or a programmable platform, including

heterogeneous components and off-chip communication. We dedicate Chapter 6 to a

discussion of streaming programmable platforms and techniques for compiling to use

their structured resources.

#### 1.4.8 Extension: Area Abstraction

With proper architectural support, streaming is a key enabler for area abstraction, which further supports design reuse and retargeting. We envision a hardware virtualization scheme, as in SCORE (Stream Computations Organized for Reconfigurable Execution) [Caspi et al., 2000a] [Markovskiy et al., 2002], whereby an arbitrarily large computation graph is partitioned and mapped onto a small, reconfigurable device as a

sequence of configurations. Buffered streams are used to decouple connected modules that are not loaded in the same configuration. If inter-configuration stream buffers are large, then each configuration can run for a long time. The resulting reduction in reconfiguration frequency allows a system to tolerate and amortize long reconfiguration delays, which are typically thousands of cycles. In contrast, non-streaming virtual platforms such as WASMII [Ling and Amano, 1993] and TMFPGA [Trimberger et al., 1997] must reconfigure at every cycle, or at best every few cycles, which requires larger, specialized reconfiguration hardware and more power.

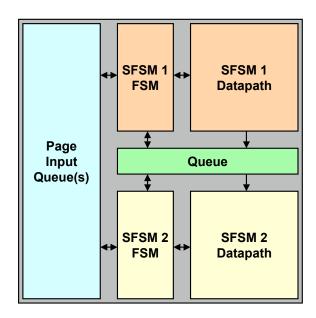

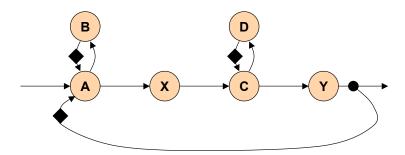

The reconfigurable fabric on a SCORE device is partitioned into fixed size slices, termed *compute pages*, communicating through a streaming network on chip. The use of compute pages facilitates scheduling and placement by providing translatable, medium granularity, units of virtualization—much like virtual memory pages. A major challenge in compiling to SCORE is partitioning the original, stream connected modules into stream connected pages, while minimizing performance overhead and area fragmentation. We discuss techniques for page partitioning in Chapter 6.

## 1.4.9 Unbounded Stream Buffering

Our streaming model, based on process networks, allows producers and consumers to decide dynamically when to read and write to streams. This approach enables a natural description of applications having dynamic communication rates or I/O sizes, such as compression/decompression. We promote the notion that intermediate data should be encoded and buffered in streams where ever possible (as opposed to being explicitly stored in shared memory or ad hoc structures—even if they are accessed through streams). This approach makes inter-module dependencies visible to the compiler, enabling more system level analysis and optimization. The actual implementation of stream buffers may be chosen by a compiler to match the resources

of the target device. A small stream buffer might be implemented in registers, whereas a large stream buffer might be implemented in memory.

Supporting dynamic rate stream access has the unfortunate consequence that programs may be specified which require unbounded buffering to function correctly. For example, a module may ignore one of its inputs for a long time, causing tokens to build up arbitrarily deep in the stream buffer. In a practical implementation with finite buffering, such programs may deadlock. This problem is not unfamiliar to RTL system designers, who in building systems with dynamic communication, must manually specify buffer implementations and sizes. In most real-world applications, dynamic buffering requirements are limited by compression formats, communication protocols, or some other constraint. Consequently, a designer can usually determine static buffer bounds by inspection or simulation.

If buffering is restricted to be in streams, then we can provide some automation for determining buffer sizes. In Chapter 5, we propose an analysis for determining minimum, deadlock-free sizes for stream buffers. If the analysis fails, a compiler can inform the designer and ask for explicit sizes on particular buffers. If buffer-related deadlock is still a concern, the implementation may detect it at runtime. A dynamically reconfigurable streaming platform such as SCORE [Caspi et al., 2000a] [Markovskiy et al., 2002] can dynamically reallocate buffers at run-time in the hopes of making additional progress after a deadlock.

## 1.5 Related Streaming Models and Architectures

The stream based design methodology proposed above is most effective for application domains that lend themselves naturally to stream decomposition. These so-called *streaming applications* are plentiful in the world of digital signal processing, media processing (audio/video), and communication. Streaming applications are typified

by:

- large, sequentially accessed data structures (data streams),

- a (mostly) persistent computation structure,

- limited and infrequent reconfiguration or mode changes, and

- limited dataflow feedback.

Such applications can often be decomposed into a series of transformations on streams, which suggests efficient implementation in hardware as a pipeline of independent modules. Feedback is typically limited to be within modules, or infrequent between modules, so that concurrency exists to evaluate many modules simultaneously. The reliance on mostly sequential data access patterns means that implementations need not be bottlenecked by large, random access memories.

A large variety of models, languages, and architectures exist to support streaming applications. We review some of them here. Additional discussion of related models is presented in Chapter 2, with a more theoretical perspective.

## 1.5.1 Statically Schedulable Dataflow

A number of existing languages and synthesis engines are based on restricted but statically schedulable streaming models, such as synchronous dataflow (SDF) [Lee and Messerschmitt, 1987b] [Bhattacharyya et al., 1996] and cyclo-static dataflow (CSDF) [Bilsen et al., 1996]. Examples include SDF to VHDL synthesis in Ptolemy [Williamson, 1998], synthesis of synchronous circuits from Simulink [Simulink, 2005], and StreamIt for RAW [Gordon et al., 2002a]. In these models, individual processes or modules repeat a firing step, or a loop of firing steps in CSDF, with each firing restricted to consume and produce a static number of tokens. The upside is that program behavior becomes fully analyzable, so that resources and schedules can be set at compile time, and simple transforms can parallelize the program to the target

hardware (e.g. horizontal and vertical graph restructuring in StreamIt). The downside is that such programs cannot represent dynamics, so they are inherently incomplete. Dynamic communication rates can only be represented by building protocols out of streams (e.g. coupling a data stream with a presence stream), and statically sized buffers may need to be allocated as special nodes. Such manual structures are cumbersome, inefficient in implementation, difficult to analyze, and obstructive to retargeting. Alternatively, coarse grained dynamics can be added by using a metalanguage to sequence a collection of statically schedulable kernels. However, the dataflow between kernels may be obfuscated in the meta-language, and system level analysis again becomes difficult or impossible. For these reasons, our streaming solution is based on a dynamic dataflow model, whose stylized dynamics are amenable to compiler analysis.

#### 1.5.2 Dynamic Dataflow

A number of models and languages exist that support dynamic flow rates on streams. Boolean controlled dataflow (BDF) [Buck, 1993], integer controlled dataflow (IDF) [Buck, 1994], and dataflow process networks (DFPN) [Lee and Parks, 1995] are dynamic rate, process network models using functional, *i.e.* stateless processes. In these models, state exists only in stream contents. This modeling style is well suited for signal processing applications, where signal flow graphs are commonplace. However, it is largely foreign to hardware designers, who are used to the expressive power of finite state machines (FSMs) and data registers. Process state may be represented as feedback streams on functional processes, but this only obfuscates state from designers and synthesis tools. It is better to treat process state differently than data streams, since state never requires queueing, and it may be optimized by a large body of existing work in sequential synthesis (*e.g.* SIS [Sentovich *et al.*, 1992]). We are not

aware of any efforts to map these stateless process models directly to hardware.

CAL [Eker and Janneck, 2003] and YAPI [de Kock et al., 2000] [Stefanov et al., 2004] are extended process network models that support process state. Our own model closely resembles CAL, with both models defining process behavior as actions guarded by process state and input presence. Both CAL and YAPI permit non-deterministic behavior which may depend on the arrival time of stream inputs. CAL does so by permitting a specification of priorities among actions, to resolve the case when multiple actions are simultaneously enabled. YAPI does so using a probe construct, which allows testing and reacting to the absence of inputs. In contrast, our model retains determinism by disallowing input testing and by constraining multiple enabled actions (as detailed in Chapter 2). These restriction ensure that behavior is faithfully retained across device generations and different implementations of stream interconnect.

The main challenge with dynamic dataflow models is that stream buffer requirements may be unbounded, and knowing whether they are unbounded is undecidable. Thus, it may be impossible for a compiler to allocate sufficient buffering resources at compile time without creating a possibility of run-time deadlock. Processor based implementations of dynamic dataflow can overcome this limitation by reallocating buffers at run-time, but hardware implementations generally cannot. Certain restricted forms of dynamic dataflow are guaranteed to need only bounded buffering, including well behaved dataflow graphs [Gao et al., 1992], BDF graphs with bounded length schedules [Buck, 1993], and CHP in static token form [Teifel and Manohar, 2004]. Our streaming approach avoids such restrictions to improve expressiveness, so it may require unbounded buffering. To bound buffers for a hardware implementation, we propose in Chapter 5 a compile-time analysis of buffer bounds based on state space enumeration. If the analysis fails to bound buffers, then we rely on a designer to bound them explicitly.

#### 1.5.3 Simulink

A number of efforts have appeared for compiling from Simulink |Simulink, 2005|, a graphical design and simulation environment, to hardware, particularly to FPGAs. Examples include Symplify DSP from Symplicity [Symplicity, 2005a], System Generator from Xilinx [Xilinx, 2005a], DSP Builder from Altera [Altera, 2005], and the BEE design environment [BWRC, 2005]. A program in Simulink is a hierarchical graph of computational nodes, where nodes process in continuous time (e.g. integrals) or discrete time (e.q. FIR filters). A library of node generators is usually provided, which generates efficient hardware implementations of non-trivial tasks such as filters or FFTs. System composition is structural and timed, so that signal connections become wires, and ideal delays become registers. This structural interpretation is unfortunate, since the subset of allowed, synthesizable behaviors is usually equivalent to SDF, a highly optimizable model (or more generally, equivalent to a collection of SDF regions with unrelated clocks, which may be optimized separately). In principle, it should be possible to apply system level optimizations such as pipelining or parallelizing by node replication. Even so, those synthesizable behaviors suffer from the same inability to express dynamics as SDF, which makes them limited for specifying complete systems.

## 1.5.4 Imperative Languages

A number of efforts have appeared for synthesizing streaming applications to hardware from imperative languages such as C (without pointers) or Java. Synthesis from a single thread of control faces a difficult challenge of extracting parallelism. Most single-thread approaches are limited to exploiting data parallelism by unrolling and mapping loops, so their performance is limited (e.g. Garp C compiler [Callahan and Wawrzynek, 2000], DEFACTO [Diniz et al., 2001], Xax [Snider, 2002]). Compaan [Turjan et al., 2005] is unique in its ability to decompose Matlab code into a network of

multiple, stream connected processes, so it can exploit a higher degree of concurrency.

Other efforts at synthesizing imperative languages make task level concurrency explicit, accepting a specification of multiple communicating threads. The most basic usage model merely uses the host language syntax and libraries to specify RTL behavior (e.g. System 1.0 OSCI, 2000, Handel-C from Celoxica [Handel-C, 2005]). More abstract approaches use the untimed semantics of communicating sequential processes (CSP) [Hoare, 1985], where inter-process connections are two-party rendezvous (e.g. Streams-C [Gokhale et al., 2000], Sea Cucumber [Jackson et al., 2003]). Typically, rendezvous is treated as a primitive from which more sophisticated mechanisms are built, such as queues or signals. Other approaches provide multiple communication abstractions, such as queues, stacks, and shared memory, and can automatically generate communication implementations (e.g. System C 2.1 OSCI, 2005), Catapult C from Mentor Graphics [Catapult C, 2005]). These approaches provide useful automation for module design, but in a sense, they provide too much freedom at the system level. The availability of multiple mechanisms for communication is intended to promote efficient implementations, but that is a moniker for manual design choices. The resulting lack of a unifying design discipline or semantic model makes system level analyses difficult, and it ultimately obstructs retargeting, reuse, and scaling on next generation devices. Even when a design discipline is enforced, the semantic model is usually non-deterministic and hard to analyze.

In contrast, we propose synthesizing a more disciplined, minimalist model of streaming. By restricting the definition of streams, we enforce a strong semantic model (process networks) with well understood properties. This streaming discipline may be embedded in many possible languages, including the ones discussed above. For example, one may restrict Streams-C to use buffered streams without signals, or SystemC 2.0 to use only FIFO queues without a capacity test (thus enforcing blocking read). Programs thus restricted would become amenable to stream specific

optimizations. Our particular choice of a process network interpretation of streaming is motivated by multiple factors, including its ability to deal with interconnect delay, and its facility in handling both static rate (e.g. signal processing) and dynamic rate (e.g. compression) problems. We revisit semantic models and our particular choices in Chapter 2.

#### 1.5.5 Streaming Architectures

A variety of architectures exist for efficient implementation of streaming multimedia applications. Examples include Cheops [Bove, Jr. and Watlington, 1995], Philips video signal processor (VSP) [de Kock, 1999], Pleiades [Wan et al., 2001], Imagine [Khailany et al., 2001], TRIPs [Sankaralingam et al., 2003], and Cell [Kahle et al., 2005]. These architectures get their performance from several key features: (1) architectural support for data streams, including efficient, sequential memory access and high throughput transfer between modules; (2) concurrent evaluation of multiple processes (though not necessarily full concurrency—some processes may be time-shared in a multi-context module such as a microprocessor); and (3) domain specific features in the modules, such as MACs (multiply-accumulate) for signal processing. Efficient sequential transfers and multi-processing are orthogonal to domain specificity, and they are present in many general purpose concurrent architectures. It has been shown that streaming can be an efficient way to use multi-processor and concurrent architectures, including Monsoon [Shaw et al., 1996], MIT RAW [Gordon et al., 2002b] [Gordon et al., 2002a], and Garp [Callahan et al., 2000].

Unfortunately, the programming models for such architectures are often ad hoc, built from an arbitrary collection of communication and concurrency mechanisms such as message passing, and lacking a unifying semantic model<sup>2</sup>. This is the same

<sup>&</sup>lt;sup>2</sup>Philips VSP [de Kock, 1999] is a refreshing example of a streaming processor whose programming model is based on a well founded, formal model of streaming, namely CSDF.

problem cited above for synthesis from C—too much freedom in the programming model. In such cases, compiler optimizations are limited to traditional, local optimizations within modules, while system optimization and correctness are left to the programmer. In some cases, strong semantic models exist for individual contexts of a subsystem but not for the control thread that sequences contextst in the subsystem. Once a program is manually partitioned and scheduled as a set of contexts, its dataflow is obscured from tools. Here again, the lack of a unifying model for total system behavior obstructs retargeting, reuse, and scaling on a next generation variant of the architecture. To address these shortcomings, we propose in Chapter 6 a set of programmable, reconfigurable architectures built expressly around our streaming discipline as a unified programming model.

## 1.6 Contribution and Organization

Our key contributions in this research work are as follows:

- 1. We present a streaming model for hardware design that, by abstracting communication timing, promotes better modular design, module reuse, and graceful handling of long interconnect delays. We provide both operational and denotational semantics (Chapter 2).

- 2. We present a concrete language TDF based on the streaming model, resembling a hardware description language with built-in streams (Chapter 2).

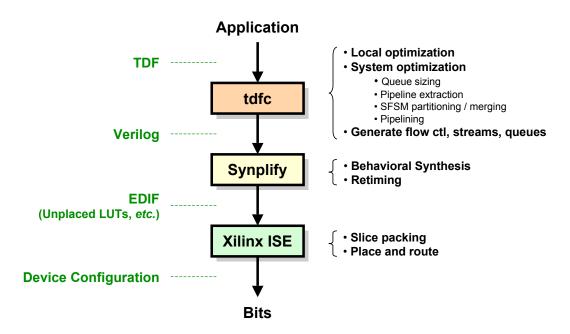

- 3. We implement a complete synthesis methodology for mapping TDF to a commercial FPGA, including automatic generation of streams and stream handshaking, as well as automatic pipelining of modules and stream interconnect (Chapter 3). We generate Verilog (RTL) as an intermediate form and rely on a

commercial back-end to map it to the FPGA. In this way, we exploit existing, state-of-the-art RTL tools.

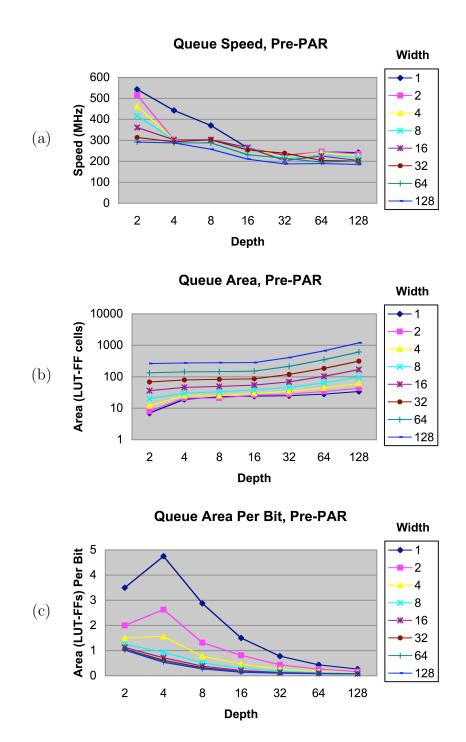

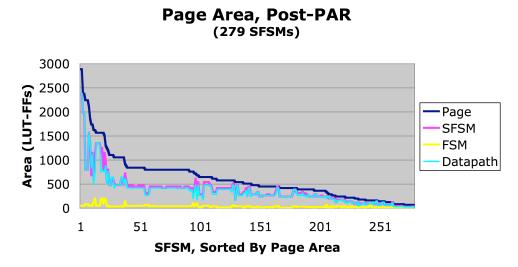

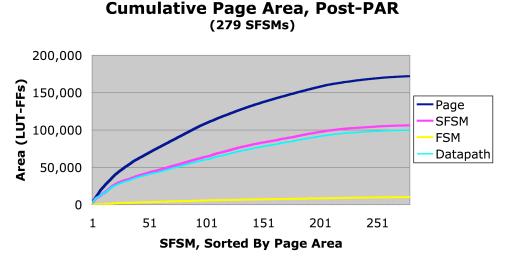

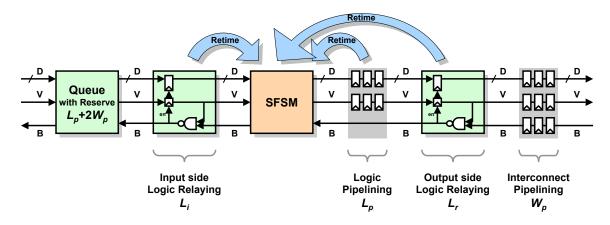

- 4. We characterize the area and performance impact of stream support on an FPGA, using the automatic synthesis methodology and seven multimedia applications written in TDF (Chapter 4).

- 5. We propose several automatic, system-level analyses and optimizations for streaming systems, including automatic selection of stream buffer sizes; selection of stream pipelining depths; stream aware, throughput-optimized placement; and serialization of non-critical modules for area reduction (Chapter 5).

- 6. We propose several streaming programmable platforms that support our streaming model more efficiently than an FPGA, and that enable better system reuse and scaling. We extend our synthesis methodology to target these platforms, including partitioning for paged platforms such as SCORE (Chapter 6).

We believe that the streaming methodology proposed herein, or something resembling it, is necessary as a next generation of design abstraction for digital systems. Our methodology addresses a number of shortcomings of the prevalent design abstractions, which are based on RTL and system composition through standard interfaces. Our methodology can be viewed as a layer of abstraction on top of RTL, mapping to it and benefiting from its existing body of compilation techniques and software.

# Chapter 2

# Language and Theoretical Foundation

This chapter presents the details of our model and language for streaming computation. The term "streaming" has many meanings in the literature, each having different expressive power, implied run-time support, and consequences for compilation tools. Our specific model and language are motivated by an intent to implement computations as digital circuits and by the associated technology trends such as growing interconnect delay. These considerations lead us to choose hardware-centric definitions for streams, modules, and system composition.

We begin this chapter with an overview of existing streaming models and their respective design considerations (Section 2.1). We then present a new model for hardware-centric streaming, TDF Process Networks (TDFPN), and give its operational semantics (Section 2.2). We present TDF (*Task Description Format*), a language for streaming applications based on TDFPN (Section 2.3). Finally, we present denotational semantics for TDFPN, which formally capture the meaning of a complete system composition (Section 2.4).

The model and language described herein were originally developed for SCORE (Stream Computations Organized for Reconfigurable Execution), targeting a dynami-

cally reconfigurable architecture [Caspi et al., 2000a]. We distinguish our model from SCORE, since we consider only single context execution ("fully spatial" execution in SCORE terms). Thus the operational semantics of TDF process networks are a subset of those of SCORE. We describe SCORE as a logical extension of TDF process networks in Chapter 6 on streaming platforms. The TDF language and its use in SCORE are fully detailed in [Caspi, 2005].

## 2.1 Streaming Models

Streaming and dataflow based design environments abound today. A short and highly incomplete list of examples might include graphical design environments such as Simulink [Simulink, 2005], Ptolemy [Ptolemy, 2005], SPW [SPW, 2005], System Studio [Synopsis, 2005] (formerly COSSAP), and LabVIEW [LabVIEW, 2005], as well as text based languages such as Streams-C [Gokhale et al., 2000], StreamIt [Gordon et al., 2002a], Silage [Hilfinger, 1985], Sisal [McGraw et al., 1985], Lucid [Ashcroft et al., 1995, and Haskell [Jones, 2003]. Additional examples may be found in [Johnston et al., 2004 and [Najjar et al., 1999]. The use of visual or textual syntax is largely irrelevant to a program's meaning, so we shall refer to both forms as languages. All these languages share a superficial similarity in defining an application as a composition of stream-connected components. Components are also termed actors, processes, nodes, or operators. Stream connections expose the communication dependencies between components, and thus their available concurrency, enabling tools to produce efficient system implementations. However, these approaches offer wildly different definitions of streams, stream access methods, component structure, notion of time, etc. Consequently, they differ in expressive power, determinism of application behavior, amenability to compiler analysis, and runtime resource requirements. We take the pragmatic approach that a programming model should provide appropriate abstractions for the underlying implementation. In this research work, we are concerned with the implementation of computation as digital circuits in Silicon, where interconnect delay is increasing with each device generation. Consequently, we seek a streaming model that can abstract communication timing while retaining deterministic behavior.

#### 2.1.1 Definitions of the Stream

Streaming languages differ, first and foremost, in their definition of the stream. That definition binds the meaning of system composition and, in turn, important system properties such as determinism and analyzability of deadlock. The general notion of a stream as a connection is insufficient, because it fails to specify important properties of the connection such as:

- Is it directional?

- Does it permit single or multiple writers?

- Does it permit single or multiple readers?

- Does it represent data values in time?

- Does it represent data values in order? (e.g. a FIFO queue does, a Petri net place [Murata, 1989] does not)

- Does it allow data values to be replicated or over-written in transit?

(e.g. a PGM graph variable [Kaplan and Stevens, 1995] allows replication and over-writing, like a register; a Streams-C signal [Gokhale, 2003] allows over-writing but not replication; a Kahn process network channel [Kahn, 1974] allows neither)

Lee and Sangiovanni-Vincentelli [Lee and Sangiovanni-Vincentelli, 1998] categorize many streaming languages into *models of computation* based on the language's definition of streams, or in their terms, of *signals*. Their models of computation in-

clude continuous time, where a signal is a function from time to value; discrete event, where a signal is set of (time, value) pairs; synchronous reactive, where a signal is a set of (quantized time, value) pairs; and process network, where a signal is an ordered sequence of values (i.e. a queue of tokens). These definitions of signals lead to a family of denotational semantics for proving properties about streaming models. We will use their categorizations for discussion here and their denotational framework later.

### 2.1.2 Notion of Time

Most of Lee and Sangiovanni-Vincentelli's models include an explicit notion of time, implying synchrony among all components. The synchrony is logical, and need not be absolute in the implementation. Nevertheless, its existence in the model would constrain any rescheduling in a parallel hardware implementation, where actors evaluate concurrently. Synchrony may become obstructive in the presence of long interconnect delay, where waiting for round trip delays would reduce performance.

The process network model is attractive for our purposes, because it abstracts away time and allows asynchrony among actors. Asynchrony is useful for dealing with long interconnect delay, so a stream consumer may be scheduled to run arbitrarily later than the stream producer. Process networks also tolerate unpredictability or changes in the timing and implementation of streams and actors. This timing independence is useful for porting designs to next generation devices, where the timing of actors and streams may be different. Another useful feature of process networks is that the queue definition of streams naturally accommodates computations where the amount of data transmitted between actors may vary dynamically, e.g. compression/decompression.

## 2.1.3 Stream Testing

A process network model, using queues for streams, may or may not allow testing stream readiness. Extended process network models such as YAPI [de Kock et al., 2000] permit an actor to test whether an input stream has data available and to take action accordingly. This approach is useful for real-time reactive systems that deal with an unreliable environment, e.g. skipping a video frame when samples are lost. However, the resulting timing dependent behavior is non-deterministic and usually difficult to debug. Traditional process network models such as Kahn process networks (KPN) [Kahn, 1974] disallow testing stream readiness. The resulting semantics, termed blocking read, require that, once an actor issues a stream read, it will block until the requested data is available. Kahn proved that this simple restriction is sufficient to guarantee deterministic behavior regardless of timing or scheduling (assuming there is no randomness within individual processes).

# 2.1.4 Dynamic Consumption / Production Rates

Streaming languages may differ in the allowed *rate* of stream access. Kahn processes may choose to consume or produce data at any time, even based on dynamic, data-dependent decisions. For example, a process may choose to ignore certain input streams, causing tokens to build up arbitrarily deep in those streams. Consequently, Kahn process networks may require unbounded buffering for streams and may dead-lock if implemented with buffers that are too small. Whether or not a particular network will deadlock is undecidable. This follows from the Turing completeness of KPN (one may build a Turing Machine in KPN using streams to implement tapes [Buck, 1993]). Deciding whether a Turing complete network will deadlock is equivalent to deciding whether it will halt, which is known to be intractable. Thus, correct execution of KPN in general requires dynamic scheduling and memory allocation.

Parks [Parks, 1995] proposes the approach of reallocating full buffers to be larger whenever a buffer related deadlock occurs. Clearly, this is impractical in a hardware implementation.

Alternatively, process networks may be restricted to avoid dynamic consumption/production rates and thus regain the decidability of memory bounds and of deadlock avoidance. In Synchronous dataflow (SDF) [Lee and Messerschmitt, 1987b], each actor is restricted to consume and produce tokens in fixed ratios, a policy enforced by associating an actor's consumption and production with an atomic *firing* step. In Cyclo-static dataflow, each actor is restricted to consume and produce tokens in a repeating pattern of fixed ratio firings. The static nature of these models permits static analyses for liveness (deadlock avoidance), memory bounds, and firing schedule. Statically schedulable models enable highly optimized mappings to arbitrary hardware, including microprocessors [Bhattacharyya et al., 1996], digital circuits [Williamson, 1998], and multi-processor arrays [Gordon et al., 2002a].

Interestingly, statically schedulable models may be extended into Turing Complete or non-deterministic models by the mere addition of certain canonical actors. Boolean controlled dataflow (BDF) [Buck, 1993] extends SDF with *switch* and *select* token routers, which are powerful enough to implement if-then-else decision making. Similarly, extending SDF with a *non-deterministic merge* yields a non-deterministic, undecidable model [Lee and Neuendorffer, 2005].

### 2.1.5 Actor Elaboration

Stream languages may allow actors to elaborate themselves into streaming subgraphs containing other actors. This elaboration is a streaming analogue of a function call, where one actor temporarily invokes another, or invokes a group of others. Static elaboration is available in most languages and corresponds simply to a hierarchy

in the stream connection graph. More interesting is dynamic elaboration, which is supported in the Kahn-MacQueen language using coroutines [Kahn and MacQueen, 1977]. Dynamic elaboration is a highly expressive mechanism, but it may make a model hard to analyze or entirely undecidable. A restricted form of dynamic elaboration is available in Heterochronous dataflow (HDF) [Girault et al., 1999], which is a statically schedulable model. Each HDF actor elaborates into a finite state machine; each state elaborates into an HDF subgraph; and so on in alternating, finite recursion. Each HDF state corresponds to a fixed consumption/production ratio, which is respected by the graph elaborated from that state. Although different states may have different ratios, the total state space is countably finite, so it corresponds to a finite number of fully-elaborated synchronous dataflow graphs.

Dynamic elaboration is not practical in a single context hardware implementation, such as an FPGA. Elaboration based on finite recursion (e.g. HDF) may be statically unrolled into hardware, but the resulting implementation will have many idle components. Efficient dynamic elaboration requires a time shared implementation, e.g. using microprocessors or dynamic reconfiguration.

# 2.2 TDF Process Networks

We now develop a particular streaming model suitable for implementing applications as digital circuits. In this section, we define the model and outline its operational semantics. In later sections, we will describe a language instance of the model and its denotational semantics.

### 2.2.1 Key Features

Determinism is a cornerstone for our model. A model is determinate or deterministic if its behavior is determined entirely by its inputs. From a technology standpoint, we desire determinism regardless of timing, so that an application will be robust to new timing characteristics when ported to a next generation device. Changes that may be appropriate when retargeting to a new device include replacing the stream transport with a new on-chip network; pipelining actors; implementing time-space trade-offs to match architectural throughput bottlenecks; and restructuring actors to match an architecturally favorable granularity. Without determinism, these changes are likely to modify system behavior and introduce bugs. With a deterministic model, a compiler is free to automatically implement any of those changes without affecting system behavior. Determinism also guarantees equivalence between hardware behavior and simulated behavior, regardless of timing and scheduling in the simulator. Thus, it enables debugging to be done in highly efficient, functional simulators.

We define the stream to be a FIFO queue as in process networks, *i.e.* a unidirectional, single producer, single consumer, first-in-first-out, buffered channel. Such a stream is an untimed abstraction of an inter-module wire, carrying a sequence of tokens from producer to consumer. We define stream access to use blocking read, so as to guarantee determinism regardless of the implementation and timing of streams and actors. An application's actors may be instantiated in hardware to run concurrently and persistently, driven by availability of input data and output space.

We wish for actors to support dynamic consumption/production rates, to naturally support compression/decompression operations. As a consequence, our model must incorporate stream buffering and allow for unbounded buffer sizes. A practical hardware implementation has only finite buffering resources and cannot support dynamic reallocation of buffers. Thus, we choose static buffer sizes for the imple-

mentation, and we accept that some programs with unbounded buffer requirements may fail. In practice, most applications have bounded requirements, even if those requirements appear to be data dependent. We will rely on compiler analysis and programmer annotation to choose static buffer sizes.

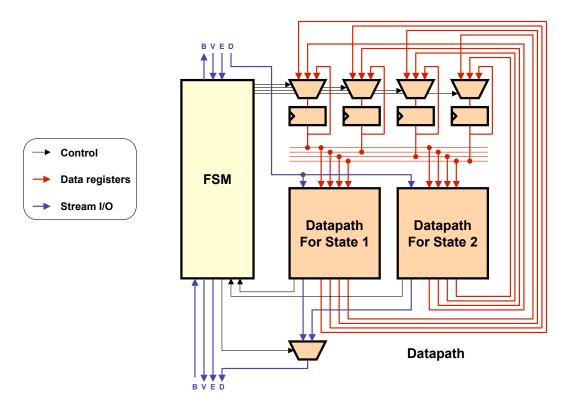

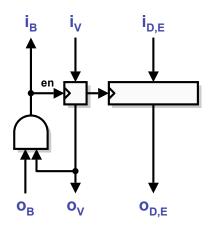

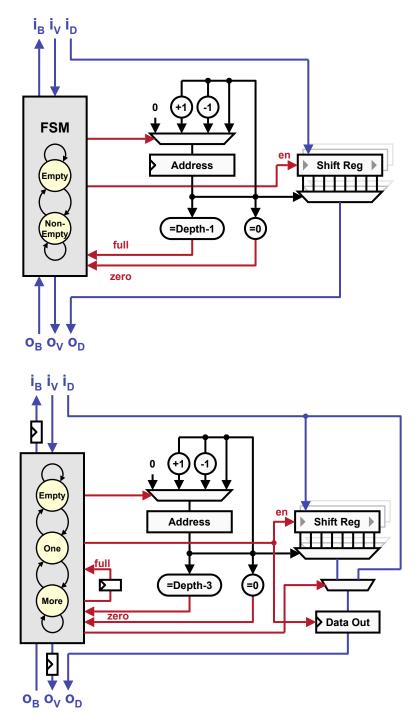

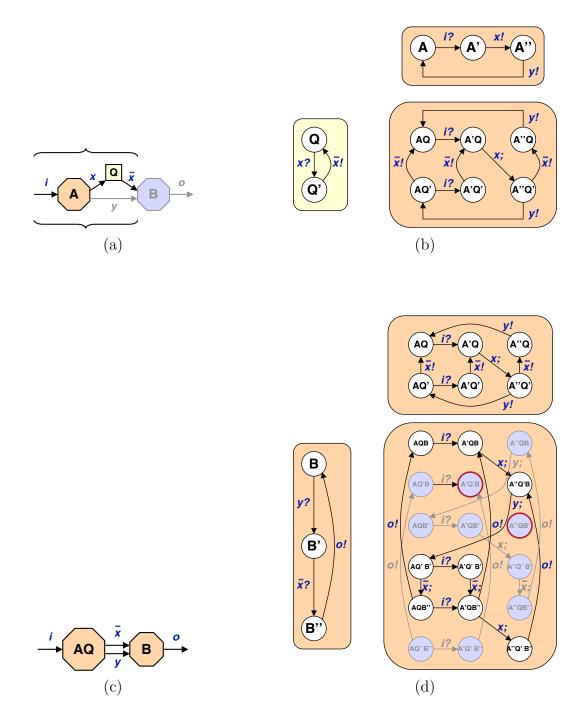

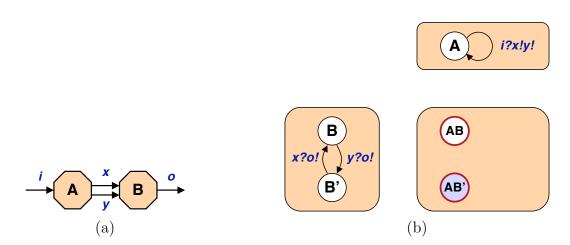

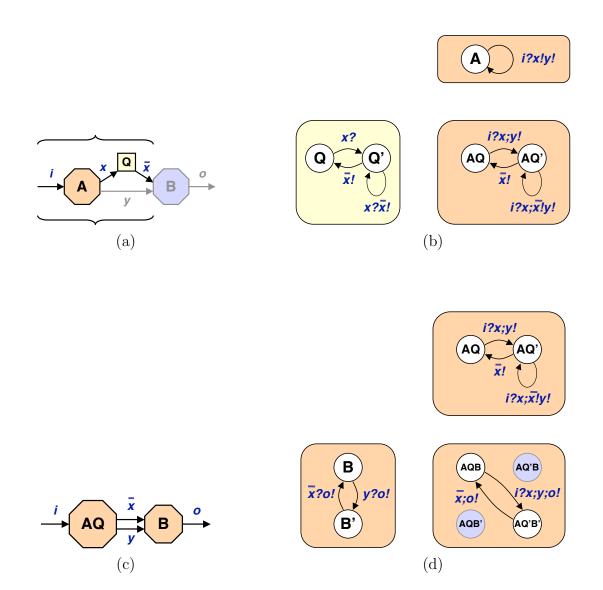

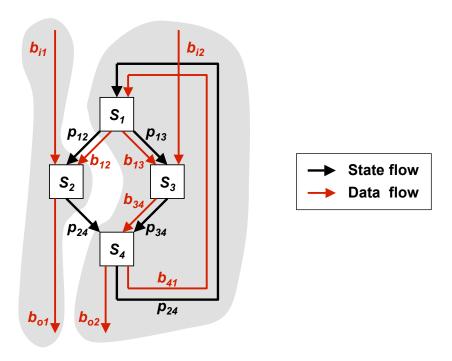

Actors should be defined in a manner familiar to hardware designers. Thus, we structure actor definitions around finite state machines (FSMs). In principle, it is possible to use functional actor definitions and add state in the form of feedback loops. However, this approach is less convenient for hardware design, and it will likely yield a poorer implementation than an FSM-based design optimized by sequential synthesis. A conventional FSM is a synchronous circuit, which evaluates inputs and sets outputs on every cycle of a clock signal. We extend that notion into a *streaming finite state machine* (SFSM), which *fires* only when input tokens and output space are available. Each state may specify which inputs and outputs are desired, comprising a state-specific *firing guard*. While the guard is unsatisfied, the actor blocks, *i.e.* stalls in the same state. When the guard is satisfied, the actor fires, *i.e.* consumes input tokens, evaluates a state-specific action, and produces output tokens.

#### 2.2.2 SFSM Definition

We begin with a simplified definition of an SFSM, presented in analogy to an FSM, and extend the definition in Sections 2.2.3 and 2.2.4. An additional restriction is discussed in Section 2.4.4.

A conventional FSM (Mealy type) may be defined as:

$$FSM = (\Sigma, \sigma_0, \sigma, I, O, f_{NS}, f_O)$$

(2.1)

where:

- $\Sigma$  is a set of states,

- $\sigma_0$  is the start state,

- $\sigma$  is the present state,

- I is the space of input values (an M-tuple of bits),

- O is the space of output values (an N-tuple of bits),

- $f_{NS}: \Sigma \times I \to \Sigma$  is the *next state* function, and

- $f_O: \Sigma \times I \to O$  is the *output* function.

At each clock cycle, the FSM samples inputs  $i \in I$ , emits outputs  $o = f_O(\sigma, i)$ , and transitions to a next state  $\sigma' = f_{NS}(\sigma, i)$ . A system is a composition of FSMs via wire connections, and all FSMs step synchronously.

To extend the above model into an SFSM, we replace I and O with tuples of sequences, rather than tuples of values. A firing guard will look ahead into the input sequences to determine whether desired inputs are available. The output function will produce output sequences.

We use a notation for sequences based on [Lee and Parks, 1995] and [Lee, 1997]. A sequence  $s \in S$  with  $S = T^{\omega}$  is a possibly infinite, ordered list of values (tokens) of type T ( $\omega$  being the first infinite ordinal). A specific sequence  $s \in S$  is denoted by a bracketed list of values  $s = [v_1, v_2, ...]$ , with  $v_i \in T$ . Let s.s' denote a concatenation of sequences s, s'. Let  $s \sqsubseteq s'$  denote that s is a prefix of s' (i.e. s' = s.s''). For tuples of sequences, using boldface, let  $s \in S^M$  denote an M-tuple, let s.s' denote a pointwise concatenation, and let  $s \sqsubseteq s'$  denote a pointwise prefix. For simplicity, we will assume that all inputs and outputs of an SFSM carry values of the same type S.

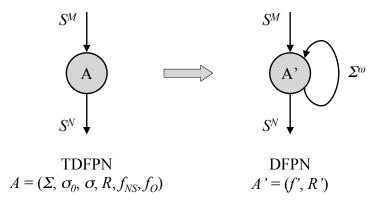

An SFSM may be operationally defined as:

$$SFSM = (\Sigma, \sigma_0, \sigma, I, O, R, f_{NS}, f_O)$$

(2.2)

where:

- $\Sigma$  is a set of states,

- $\sigma_0$  is the start state,

- $\sigma$  is the present state,

- $I \subseteq S^M$  is the space of input sequences (an M-tuple of sequences),

- $O \subseteq S^N$  is the space of output sequences (an N-tuple of sequences),

- $R: \Sigma \to I$  is a collection of *firing rules*, which specify for each state a tuple of desired input sequences,

- $f_{NS}: \Sigma \times I \to \Sigma$  is the *next state* function, and

- $f_O: \Sigma \times I \to O$  is the *output* function, producing output sequences.

An SFSM evaluates arbitrarily often. At a given evaluation, an SFSM's input queues contain subsequences  $\mathbf{i} \in I$ , and its output queues contain subsequences  $\mathbf{o} \in O$ . The SFSM fires if and only if: (1) the present state's desired inputs are available, *i.e.*  $R(\sigma) \sqsubseteq \mathbf{i}$ , or equivalently  $\mathbf{i} = \mathbf{i'}.R(\sigma)$ , and (2) the present state's outputs  $f_O(\sigma, R(\sigma))$  would fit in the output queues without overflow (in the abstract model with infinite buffering, test (2) would always be true). Upon firing, the state of the SFSM and queues are updated such that  $\sigma' = f_{NS}(\sigma, R(\sigma))$ ,  $\mathbf{o'} = \mathbf{o}.f_O(\sigma, R(\sigma))$ , and  $\mathbf{i'}$  is defined by  $\mathbf{i} = \mathbf{i'}.R(\sigma)$ . Otherwise, the SFSMs and queues retain their present state. A system is a composition of SFSMs and queues having a collective state including queue contents. A system behavior is an arbitrary interleaving of SFSM firings.

In a practical implementation, an SFSM and a queue may be able to exchange at most one token per firing. In such a case, every component sequence in R and  $f_{NS}$  would be empty or unit length, of the form [v]. Nevertheless, it is possible to accommodate longer input and output sequences in several ways, including (1) directly, using queues with windowed read/write, (2) by widening a stream into several parallel streams, or (3) by transforming multi-token states into sequences of single-token states.

## 2.2.3 Extending the Blocking Read

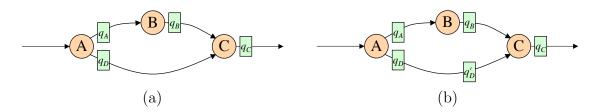

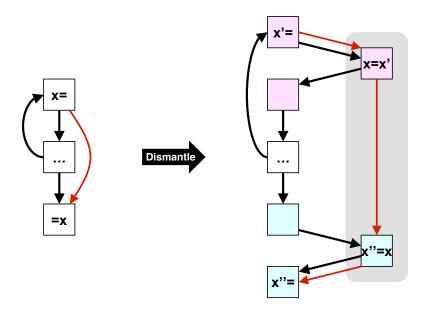

The SFSM model described above uses a multi-stream blocking read. In each state, the SFSM issues a blocking read simultaneously to every stream specified in  $R(\sigma)$ . This is a simple generalization of the Kahn-MacQueen blocking read [Kahn and MacQueen, 1977], which reads and blocks on a single stream at a time. Still, it suffers from the same non-compositionality as the Kahn-MacQueen model. A composition of two processes may not be expressible as a single process, since a single process cannot decouple the reads of the original processes. Consider, for example, the parallel composition of two identity processes, each of which copies input to output one token at a time. A process representing their composition could issue a blocking read to either of the original input streams, or to both inputs at once, but either approach couples the execution of the two processes. The single process cannot simulate, using blocking read, the original behavior of independently evaluating two processes. Likewise, the Kahn-MacQueen blocking read prevents expressing certain transformations on an SFSM, including certain decompositions into communicating sub-machines, and pipelining.

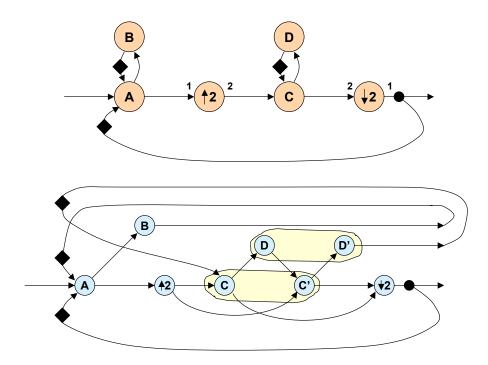

To regain compositionality, we extend the blocking read with multiple firing rules. Each state will be guarded to match one or more allowable input patterns. Each such pattern, or firing rule, may be associated with a different behavior. Thus, the above composition of two identities may issue a read that succeeds on the presence of the first input or second input, then emit a token to the first or second output accordingly. The SFSM model in equation (2.2) must be modified such that:

•  $R \subseteq \Sigma \times I$  is a set of *firing rules*, which specify for each state one or more tuples of desired input sequences.

The SFSM operational semantics are modified such that the SFSM fires in state  $\sigma$  if any of that state's firing rules are satisfied, *i.e.* if  $\exists r \in R$  s.t.  $r = (\sigma, \rho)$  and  $\rho \sqsubseteq i$ .

Unfortunately, multiple firing rules open the door to non-deterministic behavior. A process may now be sensitized to the order of arrival of its inputs, choosing a different next state depending on that order. To retain determinism, we need a strategic restriction on the structure of firing rules, output functions, and next-state functions. We defer a complete discussion of such a restriction to Section 2.4.4, where we develop denotational semantics to capture the *meaning* of a computation. Part of the solution comes from the fact that a process is not really sensitized to the order of arrival, but rather to the order of consumption. If both inputs are available, the SFSM must choose which one to consume, and that choice is an arbitrary part of the blocking read implementation. While this may seem like a source of hidden non-determinism, it in fact prevents a programmer from writing one form of timing dependent behavior. In contrast, CAL [Eker and Janneck, 2003] allows multiple firing rules to be explicitly prioritized by the programmer, representing intentional timing dependence.

# 2.2.4 Restricted Value Matching

The definition  $R \subseteq \Sigma \times I$  implies that a firing rule may match against a particular value of input, not just the presence of input. Value matching, or pattern matching, is possible in dataflow process networks (DFPN) [Lee and Parks, 1995], which are defined similarly, and in functional languages with streams such as Haskell and SML. However, our implementation of TDFPN permits only restricted value matching. The data type for each stream is extended with an end-of-stream value eos, and a firing rule may match against only two classes of values: eos or non-eos. We can redefine R as follows. For a given stream data type T, where  $S = T^{\omega}$  and  $I = S^{M}$ , let  $T^* = \{*, eos\}$ , let  $S^* = (T^*)^{\omega}$ , and let  $I^* = (S^*)^{M}$ . The symbol "\*" shall mean any non-eos value, and a rule matching "\*" shall be shorthand for a collection

of rules matching each non-eos value in the position of "\*". The SFSM model in equation (2.2) must be modified such that:

•  $R \subseteq \Sigma \times I^*$  is a set of *firing rules*, which specify for each state one or more tuples of desired input sequences.

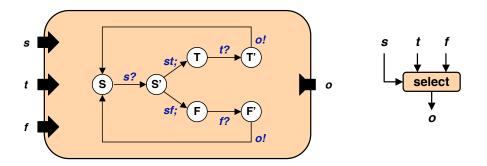

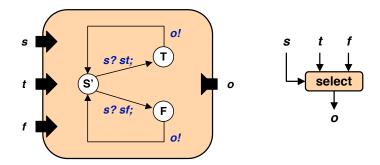

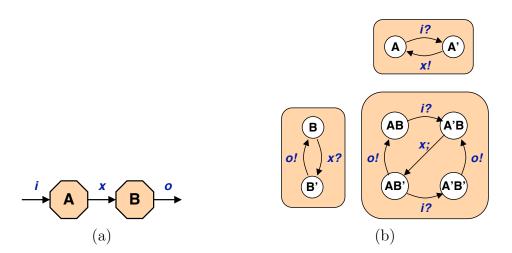

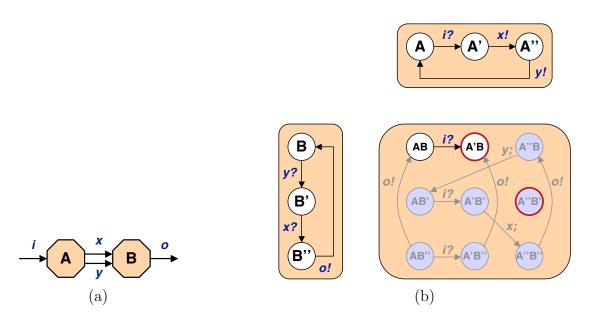

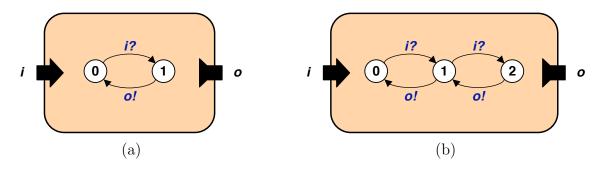

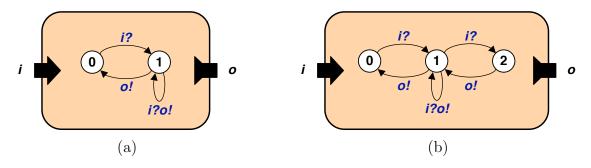

Disallowing value matching simplifies firing guards in a circuit implementation. A guard that checks for values involves comparators, whereas a guard that checks only for presence involves testing one bit. In our synthesis methodology (Chapter 3), eos is encoded as an extra data bit, so matching eos involves testing only one bit. Disallowing value matching forces certain actors to be expressed differently. Specifically, it may require stateless actors to be re-expressed with state. For example, consider the canonical select(s,t,f) actor from BDF [Buck, 1993], which selectively passes a token from either input t or f to the output, depending on the value of the boolean control token from input s. select with value matching is stateless: